Análisis del Método RBD para la Determinación de la PFD de los Elementos de una SIF

Resumen

Dentro del marco de las actividades del Ciclo de Vida de Seguridad de un Sistema Instrumentado de Seguridad, existe la necesidad de conocer el desempeño, en términos del Nivel de Integridad de la Seguridad (Safety Integrity Level SIL), de cada Función Instrumentada de Seguridad (SIF) que lo conforman. Por lo tanto, es necesario cuantificar la falla aleatoria de la función tomando en cuenta todos y cada uno de los elementos o subsistemas que están presentes en la SIF. En el presente post, se muestra como cuantificar la Probabilidad de Falla en Demanda Promedio (![]() ) de una SIF, en modo bajo demanda, realizando un análisis del método RBD (Reliability Block Diagram), como lo hace estándar IEC-61508 Parte 6.

) de una SIF, en modo bajo demanda, realizando un análisis del método RBD (Reliability Block Diagram), como lo hace estándar IEC-61508 Parte 6.

1. Introducción

Cuando los procesos o sistemas críticos que se utilizan en la industria nuclear, química, petróleos, etc no son apropiadamente controlados o mantenidos pueden dejar de funcionar y, en algunos casos, llevar al Proceso Bajo Control (EUC) a un riesgo significativo para la seguridad de personas, medio ambiente y financiero. Los Sistemas Instrumentados de Seguridad o SIS, como se les conoce, son sistemas diseñados para reducir el riesgo del proceso cuando existen desviaciones de sus variables o malfuncionamiento de algún equipo o instrumento.

El hardware de un SIS está compuesto principalmente por tres subsistemas, subsistema de sensado, subsistema de resolvedor lógico y subsistema de actuación; como se muestra en la figura 1. El subsistema de sensado monitorea el proceso crítico, examinando condiciones potencialmente inseguras; el resolvedor lógico interpreta las entradas del subsistema de sensado y ejecuta determinadas acciones mediante el subsistema de actuación.

El estándar IEC-61508, publicado en el año 1997 y actualizado en 2010, ha sido adoptado por muchos países como una norma de carácter nacional. En este se muestran 2 conceptos muy importantes: el Ciclo de Vida de Seguridad y el Nivel de Integridad de la Seguridad (Safety Integrity Level, SIL). Como procedimiento dentro del Ciclo de Vida de Seguridad es necesario realizar la cuantificación de la falla aleatoria que, comúnmente, se conoce como verificación del SIL, de cada SIF que conforman al SIS, de tal manera de confirmar que la Probabilidad de Falla en Demanda promedio ( ) del hardware diseñado cumple con el Factor de Reducción de Riesgo requerido por el proceso. En caso de no cumplir este requerimiento es necesario realizar una modificación a dicho hardware hasta cumplir con la Reducción de Riesgos necesaria. El proceso de demostración que la SIF cumple con los requisitos de la aplicación, toma en cuenta, además, las restricciones de hardware definidas en la norma IEC-61508 y IEC-61511 y la Capacidad Sistemática del hardware utilizado.

) del hardware diseñado cumple con el Factor de Reducción de Riesgo requerido por el proceso. En caso de no cumplir este requerimiento es necesario realizar una modificación a dicho hardware hasta cumplir con la Reducción de Riesgos necesaria. El proceso de demostración que la SIF cumple con los requisitos de la aplicación, toma en cuenta, además, las restricciones de hardware definidas en la norma IEC-61508 y IEC-61511 y la Capacidad Sistemática del hardware utilizado.

Fig. 1 Hardware de Sistema Instrumentado de Seguridad

El proceso de verificación del SIL puede ser abordado mediante diferentes metodologías, todas basadas en técnicas de análisis probabilístico y entre las más conocidas están: Análisis de Árbol de Fallas (FTA), Análisis Modos de Falla y Eventos (FMEA), Diagrama de Bloques de Confiabilidad (RBD), Análisis de Markov, técnicas mixtas, etc. El uso de cada técnica tiene sus ventajas y desventajas.

2. Probabilidad de Falla en Demanda

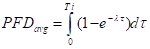

Es una medida que está definida como la probabilidad de que la SIF no pueda cumplir con la intención para la cual fue diseñada, en otras palabras, es la probabilidad con la cual la SIF es incapaz de desempeñar su función de seguridad; lo que significa que la SIF esta inhabilitada para responder a una demanda y no podrá iniciar ninguna acción de seguridad. La PFD indica un valor instantáneo, para su uso en seguridad funcional es necesario expresar como  la cual indica un valor promedio sobre el intervalo de prueba de la SIF

la cual indica un valor promedio sobre el intervalo de prueba de la SIF

; (1)

; (1)

Hay que considerar que la ![]() es una función de la tasa de fallas

es una función de la tasa de fallas  , la tasa de reparación

, la tasa de reparación  , el Intervalo de prueba

, el Intervalo de prueba  ,

,

las fallas de causa común  , entre otros.

, entre otros.

Para satisfacer los requerimientos dados en la Especificaciones de los Requerimientos de la Seguridad (SRS) de la SIF con un SIL objetivo obtenido del análisis de riesgo del proceso, la  de la SIF diseñada debe ser menor al valor límite indicado en la tabla 1, según sea el caso.

de la SIF diseñada debe ser menor al valor límite indicado en la tabla 1, según sea el caso.

Tabla 1. SIL y  según IEC-61508.

según IEC-61508.

|

Nivel de Integridad de Seguridad (SIL) |

Probabilidad de Falla en |

Reducción de Riesgo |

|

4 |

≥10−5 a <10−4 |

>10.000 a ≤100.000 |

|

3 |

≥10−4 a <10−3 |

>1.000 a ≤10.000 |

|

2 |

≥10−3 a <10−2 |

>100 a ≤1.000 |

|

1 |

≥10−2 a <10−1 |

>10 a ≤100 |

3. Diagrama de Bloques de Confiabilidad (RBD)

Es una técnica gráfica de análisis, la cual expresa como está conectado un sistema y el número de componentes de acuerdo a una relación lógica de confiabilidad.

Los componentes conectados en serie representan una conexión lógica “and” y los conectados en paralelo son representados mediante la conexión “or”, mientras que, la combinación de componentes en serie y paralelo representa lógica de votación. Un esquema RBD tiene un orden de análisis, siempre va de izquierda a derecha, y desde el nodo más a la izquierda hacia el nodo más a la derecha se presentarán las

trayectorias o rutas para una operación exitosa del sistema (representa una medida de éxito). Cuando un componente falla, este cortará la conexión o ruta correspondiente, a medida que ocurren las fallas en los componentes, el sistema seguirá operando o funcionando hasta que no exista una ruta o vía válida desde el nodo más a la izquierda al nodo más a la derecha y, la probabilidad de falla del sistema en estudio se puede calcular o determinar de acuerdo a principios probabilísticos; por ejemplo: sea un subsistema con votación 1oo2, esto significa que dispone de 2 canales diferentes con sus propios componentes, es decir, independientes, y se requiere que con 1 canal disponible todavía puede ser confiable y cumplir con su intención de diseño; sin embargo, está claro que podría darse una falla de causa común que afectaría a ambos componentes y en esa circunstancia, el sistema deja de ser confiable, por lo que, ante una demanda él no podrá llevar al proceso a modo seguro, tal esquema se muestra en la siguiente figura:

Fig. 2 RBD para un esquemade votación 1oo2 de sensores

Para el presente documento se consideran las siguientes suposiciones para el uso del Enfoque RBD:

a) La  resultante de un subsistema es menor que 10 -1 (Modo Bajo Demanda) y también la PFH es menor a 10 -5 (Modo Alta Demanda y Modo Continuo).

resultante de un subsistema es menor que 10 -1 (Modo Bajo Demanda) y también la PFH es menor a 10 -5 (Modo Alta Demanda y Modo Continuo).

b) La tasa de falla y reparación de los componentes se consideran constantes dentro del tiempo de vida del sistema.

c) La tasa de falla de hardware utilizado como información para el cálculo se considera para subsistemas con canales simples.

d) Todos los canales en un grupo de votación tienen la misma tasa de falla y la misma tasa de cobertura de diagnóstico.

e) La tasa de falla de hardware total de un canal en un subsistema es la suma de la tasa de fallas peligrosas y la tasa de fallas seguras y se asume iguales.

f) La prueba o test y reparación para cada función de seguridad es completa (perfecta). Esto significa que todas las fallas que permanezcan sin detectar son detectadas por la prueba o test.

g) El intervalo de prueba es por lo menos una orden de magnitud mayor que el intervalo de test de diagnóstico.

h) No se considera el estudio del efecto de la tasa de demanda y el intervalo esperado entre la demanda.

i) Para cada subsistema hay un único intervalo de prueba y un tiempo medio para la restauración.

j) Se considera que se encuentra disponibles múltiples grupos de reparación para trabajar en todas las fallas conocidas.

k) El intervalo esperado entre las demandas es por lo menos un orden de magnitud mayor que el tiempo medio para la reparación.

3.1 Autodiagnóstico, Fracción de Falla Segura y Tiempo Medio Improductivo (MDT)

Hoy en día, muchos equipos pueden detectar fallas por sí mismos mediante el denominado diagnóstico; esta característica o capacidad en un equipo se denomina Cobertura de Diagnóstico (DC) y en ningún caso puede detectarse la totalidad de las fallas, es decir, que el DC nunca llega al 100%. Ahora la tasa de falla total de un equipamiento  , tal como lo muestra la figura, se divide en fallas seguras

, tal como lo muestra la figura, se divide en fallas seguras  y fallas peligrosas

y fallas peligrosas  , las mismas se dividen en seguras detectadas

, las mismas se dividen en seguras detectadas  , seguras no detectadas

, seguras no detectadas  , así como, en peligrosas detectadas

, así como, en peligrosas detectadas  y peligrosas no detectadas

y peligrosas no detectadas  Las tasas de falla seguras son justamente las que llevan a modo seguro; por otro lado, las fallas peligrosas pueden detectarse mediante diagnóstico y justamente coincide con el criterio de la cobertura de diagnóstico definido anteriormente. Por lo tanto, las fallas peligrosas no detectadas son aquellas que debemos estudiar y determinar y este valor es el que nos indica cuán confiable es el equipo para las aplicaciones de seguridad. La norma IEC-61508 introduce el término fracción de falla segura SFF definido como:

Las tasas de falla seguras son justamente las que llevan a modo seguro; por otro lado, las fallas peligrosas pueden detectarse mediante diagnóstico y justamente coincide con el criterio de la cobertura de diagnóstico definido anteriormente. Por lo tanto, las fallas peligrosas no detectadas son aquellas que debemos estudiar y determinar y este valor es el que nos indica cuán confiable es el equipo para las aplicaciones de seguridad. La norma IEC-61508 introduce el término fracción de falla segura SFF definido como:

;

;

(2)

para identificar las características de confiabilidad de un determinado dispositivo que será utilizado de una Función Instrumentada de Seguridad.

Fig.3 División de la tasa de fallas total

La probabilidad de falla en demanda está relacionada con las fallas peligrosas  que evitan que el SIS funcione cuando se precise que así lo haga; es decir, ante una demanda. En el análisis se puede considerar que para cada SIF existe una prueba de funcionamiento periódica en un tiempo Ti y también existe una reparación perfecta, por lo que todas las fallas no detectadas se descubren

que evitan que el SIS funcione cuando se precise que así lo haga; es decir, ante una demanda. En el análisis se puede considerar que para cada SIF existe una prueba de funcionamiento periódica en un tiempo Ti y también existe una reparación perfecta, por lo que todas las fallas no detectadas se descubren

mediante una prueba periódica de la SIF. Cuando se produce una falla, se presupone que en promedio ocurre en el punto intermedio del intervalo de prueba periódica; en otras palabras, la falla sigue sin detectarse durante el 50% del período de prueba. Tanto para fallas peligrosas no detectadas y peligrosas detectadas, el tiempo medio improductivo o MDT depende del intervalo de prueba Ti, el tiempo medio de reparación MTR y del tiempo medio hasta el restablecimiento

MTTR.

4. Cálculo de la PFDavg mediante RBD

4.1 Arquitectura 1oo1

Esta arquitectura consiste de un solo canal, sin embargo, como nuestro análisis está centrado al estudio de las fallas peligrosas y estas se dividen en fallas peligrosas detectadas y fallas peligrosas no detectadas, al tener diferentes tasas de falla cada una es necesario agrupar estas fallas en una arquitectura en serie, tal como lo muestra la figura, donde  representa el bloque de fallas peligrosas no detectadas (las más peligrosas) y

representa el bloque de fallas peligrosas no detectadas (las más peligrosas) y  las fallas peligrosas detectadas. Ambas dan como resultado el denominado tiempo medio improductivo

las fallas peligrosas detectadas. Ambas dan como resultado el denominado tiempo medio improductivo  cuya

cuya

tasa de falla es  y es posible calcularlo sumando los tiempos medios improductivos en directa proporción respecto a la contribución de la probabilidad de falla del canal, es decir:

y es posible calcularlo sumando los tiempos medios improductivos en directa proporción respecto a la contribución de la probabilidad de falla del canal, es decir:

;

;

(3)

;

;

(4)

Fig.4 Arquitectura RBD para un esquema 1oo1

Ejemplo:

Sea un elemento del cual se desea obtener la  para diferentes valores de la cobertura de diagnóstico DC y se conoce que la tasa de

para diferentes valores de la cobertura de diagnóstico DC y se conoce que la tasa de

fallas peligrosa es  , el tiempo de reparación es igual al tiempo de restablecimiento

, el tiempo de reparación es igual al tiempo de restablecimiento  .

.

Mediante el uso de la ecuación 4, se puede observar además que la  aumenta conforme aumenta el Intervalo de prueba

aumenta conforme aumenta el Intervalo de prueba  y reduce conforme aumenta el porcentaje de la Cobertura de Diagnostico.

y reduce conforme aumenta el porcentaje de la Cobertura de Diagnostico.

4.2 Arquitectura 1oo2

Esta arquitectura consiste en dos elementos conectados en paralelo, de tal manera que cualquier canal puede ejecutar la función de seguridad, por lo tanto, debería existir una falla peligrosa en ambos canales antes de que la función de seguridad falle bajo una demanda. Se supone que cualquier test de diagnóstico solo reportará las fallas encontradas y no cambiará a ningún estado su salida ni la votación especificada. La figura muestra el RBD para dicha arquitectura donde  ,

, pertenecen al equipamiento o componente 1 y

pertenecen al equipamiento o componente 1 y ,

,  al equipamiento o componente 2.

al equipamiento o componente 2.

Fig. 5 Arquitectura RBD para un esquema 1oo2

Por otro lado, el RBD contiene un bloque en serie adicional que representa las fallas de causa común considerando que los equipos en paralelo son similares, este bloque denota la fracción de fallas no detectadas que tienen causa común  . Ahora, para el caso de fallas detectadas por diagnóstico de causa común

. Ahora, para el caso de fallas detectadas por diagnóstico de causa común  . Estos valores son fracciones que se consideran igual entre 5% al 10% del total de fallas peligrosas del equipamiento.

. Estos valores son fracciones que se consideran igual entre 5% al 10% del total de fallas peligrosas del equipamiento.

El tiempo medio improductivo MDT para esta arquitectura está definida como:

;

;

(5)

Donde  es el tiempo improductivo de cada elemento o equipamiento y se nota que con esta arquitectura el tiempo de parada del conjunto

es el tiempo improductivo de cada elemento o equipamiento y se nota que con esta arquitectura el tiempo de parada del conjunto  se reduce a la mitad de

se reduce a la mitad de  .

.

Cuando un canal o elemento falla de forma peligrosa, el conjunto pasa a un estado de operación degradada y, aun así, puede desempeñar la función de seguridad especificada ante una demanda con el que queda operando, si este segundo elemento falla de forma peligrosa entonces todo el grupo falla y la función no podrá ejecutar la función de seguridad.

La  , según indica IEC-61508 Parte 6, considerando efectos de fallas de causa común es:

, según indica IEC-61508 Parte 6, considerando efectos de fallas de causa común es:

;

;

(6)

Ejemplo:

El resultado de la tabla nos indica un resultado similar al anterior, sin embargo, se puede ver la  se reduce notablemente cuando se utiliza arquitectura con votación.

se reduce notablemente cuando se utiliza arquitectura con votación.

4.3 Arquitectura 2oo2

Esta arquitectura consiste en dos elementos conectados en serie, por lo tanto, ambos canales son necesarios para ejecutar la función de salida ante una demanda. La figura muestra el RBD para la arquitectura 2oo2; donde, la  está dada por:

está dada por:

; (7)

; (7)

Fig. 6 Arquitectura RBD para un esquema 2oo2

Ejemplo

Esta arquitectura no dispone mejor  que la que tiene 1oo1.

que la que tiene 1oo1.

4.4 Arquitectura 2oo3

Esta arquitectura consiste en tres elementos conectados en paralelo con un arreglo de votación mayoritario para la salida de la señal, la misma no cambiará si solo un elemento presenta un resultado diferente o en desacuerdo con los otros dos elementos. Sin embargo, en temas de seguridad, para que la función esté disponible, con la falla de un elemento la función puede permitir la activación de la salida de votación pasando a modo de operación degradado, si existiera una segunda falla entonces esta arquitectura no puede ejecutar la función de salida; por lo tanto, no estará disponible la SIF.

La figura 7 y 8 muestran la arquitectura para una votación 2oo3.

Fig. 7 Arquitectura RBD para un esquema 2oo3

Fig. 8 Arquitectura RBD para un esquema 2oo3

; (8)

; (8)

; (9)

; (9)

; (10)

; (10)

Ejemplo

Vemos como la  para esta arquitectura es menor que la 1oo2.

para esta arquitectura es menor que la 1oo2.

5. Conclusiones

Hemos observado como la metodología RBD puede ser aplicada para la determinación cuantitativa de la  de los elementos que participan en una SIF; aun cuando se encuentran en configuración de votación.

de los elementos que participan en una SIF; aun cuando se encuentran en configuración de votación.

El modelo de RBD refleja la estructura de confiabilidad del sistema o subsistema en estudio; es intuitivo y relativamente fácil de desarrollar.

Un siguiente paso es abordar el estudio de arquitecturas de votación como 1oo3, 2oo4; y cuando disponen de diagnóstico como 1oo2D, oo3D.

6. Bibliografía

|

[1] |

Guo H., Yang X. “A simple reliability block diagram |

|

[2] |

Creus A., “Fiabilidad y Seguridad”, Marcombo Ediciones |

|

[3] |

Fernandez I. et al. “Sistemas Instrumentados de |

|

[4] |

Magnetrol. “Understanding Safety Integrity level” |

|

[5] |

IEC 61508. “Functional safety of electrical/electronic/programable |

|

[6] |

IEC 61511. “Functional safety” safety instrumented systems |

Raúl Roque

Santa Cruz – Bolivia

FSEng TÜV SÜD TP18051528

Romel Rodriguez

Functional Safety Expert TÜV SÜD TP18010990 | ISA84/IEC 61511 Expert | FSEng TÜV Rheinland 575/07 | PHA Leader

Análisis del Método RBD para la Determinación de la PFD de los Elementos de una SIF Leer más »